# **Efficient of Noise and Energy of CMOS Amplifier for Neural Recording Applications**

<sup>1</sup>G. Vasantha, <sup>2</sup>Babitha, <sup>3</sup>Y. Harshavardan Raju, <sup>4</sup>Kaveri, <sup>5</sup>Gowrinandini <sup>1</sup> Assistant Professor, Department of ECE, AITS Tirupati <sup>2345</sup>B.Tech Student, Department of ECE, AITS Tirupati,

<sup>12345</sup>Email: vasantharoy@gmail.com, babithareddy99@gmail.com, yellamarajuharsha@gmail.com, kaveripulluru@gmail.com, nandini19981995@gmail.com

#### Abstract-

Inside neural checking frameworks, the front-end speaker shapes the basic component for flag identification and preprocessing, which decides the loyalty of the biosignal, as well as effects control utilization and indicator estimate. In this paper, a novel joined criticism circle controlled methodology is proposed to make up for info spillage flows created by low commotion speakers when in coordinated circuit shape close by flag spillage into the information inclination arrange. This circle topology guarantees the Front-End Amplifier (FEA) keeps up high info impedance over all assembling and operational varieties. In the proposed strategy displays a low power and low clamor neural speaker IC for handling both activity potential and nearby field potential flags in neural embed gadgets. In view of a capacitive input topology, the center operational trans-conductance speaker uses a two-organize structure with current cushion accomplishing wide data transmission, expansive yield swing, and little region. The proposed neural speaker is planned utilizing 1µm CMOS process and accomplishes 5.268dB gain.

Index terms - neural amplifier; neural recorder; feedback; trans-conductance capacitive operational amplifier, CMOS technology, low-noise amplifiers, neural recording.

### I. INTRODUCTION

The Front-End Amplifier (FEA) is a key component for flag identification inside neural action observing frameworks [1], [2]. Developing enthusiasm for the field of neuroscience has quickened examination into such frameworks. Be that as it may, these are confined by an absence of reasonable Integrated Circuit (IC) systems [3], [4]. A coordinated FEA inside a little chip zone empowers neuroscientists and clinicians to at the same time record and watch bigger varieties of neural information, utilizing different cathodes and multichannel checking frameworks [5]- [7]. Further, procuring neural movement information by means of high-thickness exhibit detecting empowers future research in infection and neuro prosthetic gadgets [8]. Electrically-noticeable signs produced by neural action are low in both sufficiency and recurrence. Regularly, the flag is included two parts, the Action Potential (AP)— otherwise called neural spikes—and the Local Field Potentials (LFP). APs have amplitudes running from 5 µVpp to 50 µVpp, crosswise over frequencies of 300 Hz to 7.5 kHz, while LFP amplitudes are around 1 mVpp to 10 mVpp, over a scope of 25 mHz to 100 Hz, as portrayed in [3].

A neural recorder is an implantable restorative gadget used to gather neural signs for watching and diagnosing certain side effects of different maladies related with the mind, and to investigate the signs of the cerebrum identified with physical action [1]. Specifically, neural signs known as activity potential (AP). which live in the recurrence band from 300 Hz to around 7 kHz, and nearby field potential (LFP) which is seen around 1 Hz to 300 Hz frequencies, are of intrigue. These are extremely frail signs with amplitudes running from 100 μVpp up to 1 mVpp. In this manner, it is vital to give adequate intensification preceding further preparing of the flag, and to limit the expansion of clamor in the meantime. To interface the neural chronicle IC with multi-cluster test for high-goals handling, control utilization is additionally essential as it might cause temperature rise and lead to tissue harm. The neural intensifier is the primary square in the neural account chain and is basic in choosing the general execution of the chronicle gadget. This paper shows a low-power and low-commotion speaker for neural account frameworks.

This paper is organized in five sections. After this introduction, in Section II, existing method discussed of the paper Section III about the proposed method explained, as well as the novel feature of the proposed method. Finally, Sections IV and V provide the simulation results and the conclusions, respectively

### **II.EXISTING SYSTEM**

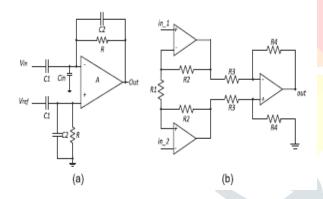

Customarily in neural observing frameworks, the instrumentation enhancer was broadly utilized for Printed Circuit Board (PCB) scale frameworks because of its high info impedance and simplicity of gain alteration utilizing outer resistors, as appeared in Fig. 1(b). In any case, it isn't appropriate for implantable gadgets because of its substantial shape factor [13]. The idea of a solitary IC kick the bucket supporting a reduced yet high-number exhibit of sensors conquers this, empowering valid in-vivo neural checking [14], [15]. To nullify the vast chip region of resistors, as appeared in Fig. 1(a), capacitive input (CF) is commonly utilized, as it arranges the gain by the proportion of capacitors, while at the same time dismissing the DC counterbalance [16]. This strategy has turned into a most well known topology in neural detecting applications [17], [18]. A huge info impedance might be accomplished by choosing a little info capacitance, C1 in Fig. 1(a), to diminish flag weakening for low recurrence neural applications. The information impedance of this topology is, in any case, restricted by the Operational Amplifier (Op-amp) structure, because of the info entryway spillage current. Additionally, a low commotion Op-amp requires a moderately huge geometry input door, as the glimmer (1/f) clamor is contrarily corresponding to the transistor's territory. Substantial gadgets yield a huge parasitic capacitance, bringing about an expansion in the spillage current.

Figure 1. (a) Circuit topology of capacitive feedback biasing. (b) Structure of conventional instrumentation amplifier.

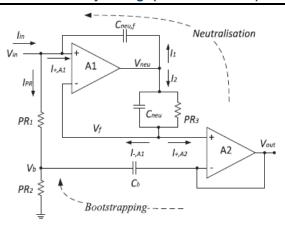

In Fig. 2, the FEA includes two low-noise two stage Complementary Metal-Oxide Semiconductor (CMOS) amplifiers (A1 and A2, details discussed in Section II-B) and two feedback loops, one each for neutralization (to address the leakage current of amplifier) and bootstrapping (to address current into bias network). Pseudo Resistors (PR) is used in the design. The PR, as shown in Fig. 4(b), comprises two Metals-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) back-to-back, to create a large resistance with acceptable layout area [25]. Bootstrapping [23] is a voltage feedback loop technique to minimize the signal current entering PR1.

Figure 2. Circuit topology of FEA design with bootstrapping and neutralization loop.

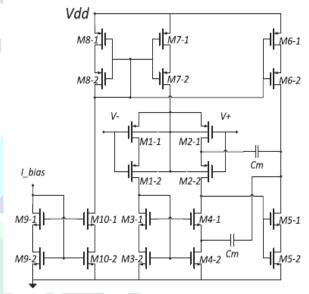

Figure 3. Circuit schematic of CMOS low noise two-stage Op-amp.

## A. Low Noise Two-Stage Op-Amp Design

clamor Lower input-alluded in IC Op-amp configuration, as appeared in Fig. 3, is accomplished by expanding the measure of the enhancer's cascoded input gadgets (M1 - 1,M1 - 2,M2 - 1,M2 - 2). The Op-amp includes two phases with Miller pay. In the primary stage, PMOS differential matches in a disengaged Nwell are picked because of the inborn lower 1/f commotion over N-channel MOS (NMOS). Other transistor masses (back entryways) are associated with the fitting rails (not expressly appeared for lucidity). The cascode structure builds the open circle gain (AOP) without expanding current utilization or clamor [27], [28]. M6\_1, 2, M7\_1, 2, M8\_1, 2, M9\_1, 2, and M10\_1, 2 are current mirrors driven by a reference inclination current. These fell mirrors increment the dynamic load protection from increment the gain of enhancer.

#### III. PROPOSED SYSTEM

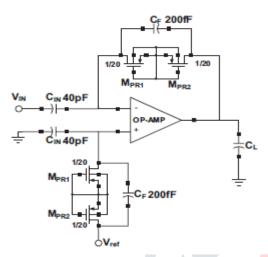

Figure 4 shows the block diagram of the designed neural amplifier. It uses an operational transconductance intensifier (OTA) with capacitive-criticism. The capacitive-criticism topology empowers precise gain setting, where the mid-band gain AM is controlled by the proportion CIN/CF. Likewise; AC coupling is utilized so as to expel the huge DC balance voltage, brought about by the substance response at the terminal neuron interface.

Figure 4. Block diagram of the designed neural amplifier

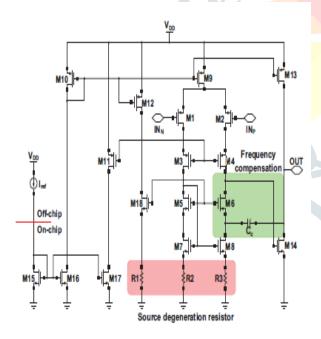

Figure 5. Schematic of operational trans-conductance amplifier

In this plan, the gain is chosen to be around 46 dB utilizing the estimations of CIN=40 pF and CF=200 fF. The low-pass data transfer capacity of the enhancer is roughly equivalent to Gm/(AM•CL) where Gm is transconductance of the OTA. The low-pass cutoff must be set to be sufficiently high to help AP signals. The sub-Hertz high pass cut-off recurrence is controlled by  $1/(2\pi$

•RP•CIN), where RP is a vast opposition comprising of MPR1 and MPR2 going about as a pseudo-resistor. Figure 2 exhibits the circuit schematic of the proposed OTA. Among a few topologies accessible in the plan of the OTA, this work uses a two-arrange.

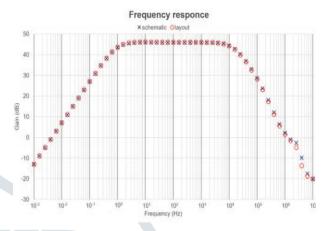

Figure 6. Frequency 4 response of neural amplifier

Figure 6 shows the frequency response of the neural amplifier. It measured gain on x-axis and frequency on y-axis.

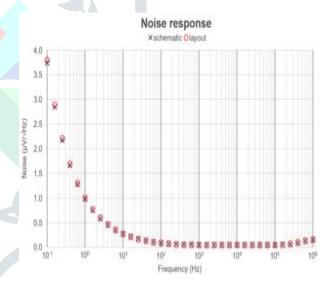

Figure 7. Noise performance of neural amplifier

Figure 7 shows the frequency response of the neural amplifier. It measured noise on x-axis and frequency on y-axis.

#### REFERENCESS

[1] R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," IEEE J. Solid-State Circuits, vol. 38, no. 6, pp. 958–965, Jun. 2003.

[2] W. Wattanapanitch, M. Fee, and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier,

- " IEEE Trans. Biomed. Circuits Syst., vol. 1, no. 2, Jun. 2007

- [3] G. Palmisano and G. Palumbo, "A compensation strategy for two-stage CMOS opamps based on current buffer," IEEE Trans. Circuits Syst. I, vol. 44, no. 3, pp. 257–262, Mar. 1997

- [4] P. Kmon and P.gryboś, "Energy efficient low-noise multichannel Neural amplifier in submicron CMOS process," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 7, pp. 1764–1775, Jul. 2013

- [5] Yi Chen, A. Basu, L. Liu, X. Zou, R. Rajkumar, G. S. Dawe, and M. Je "A digitally assisted, signal folding neural recording amplifer," IEEE Trans. Biomed. Circuits Syst., vol. 8, no. 4, pp. 528–542, Aug. 2014.